H.264 Encoder: High-Performance Video Compression

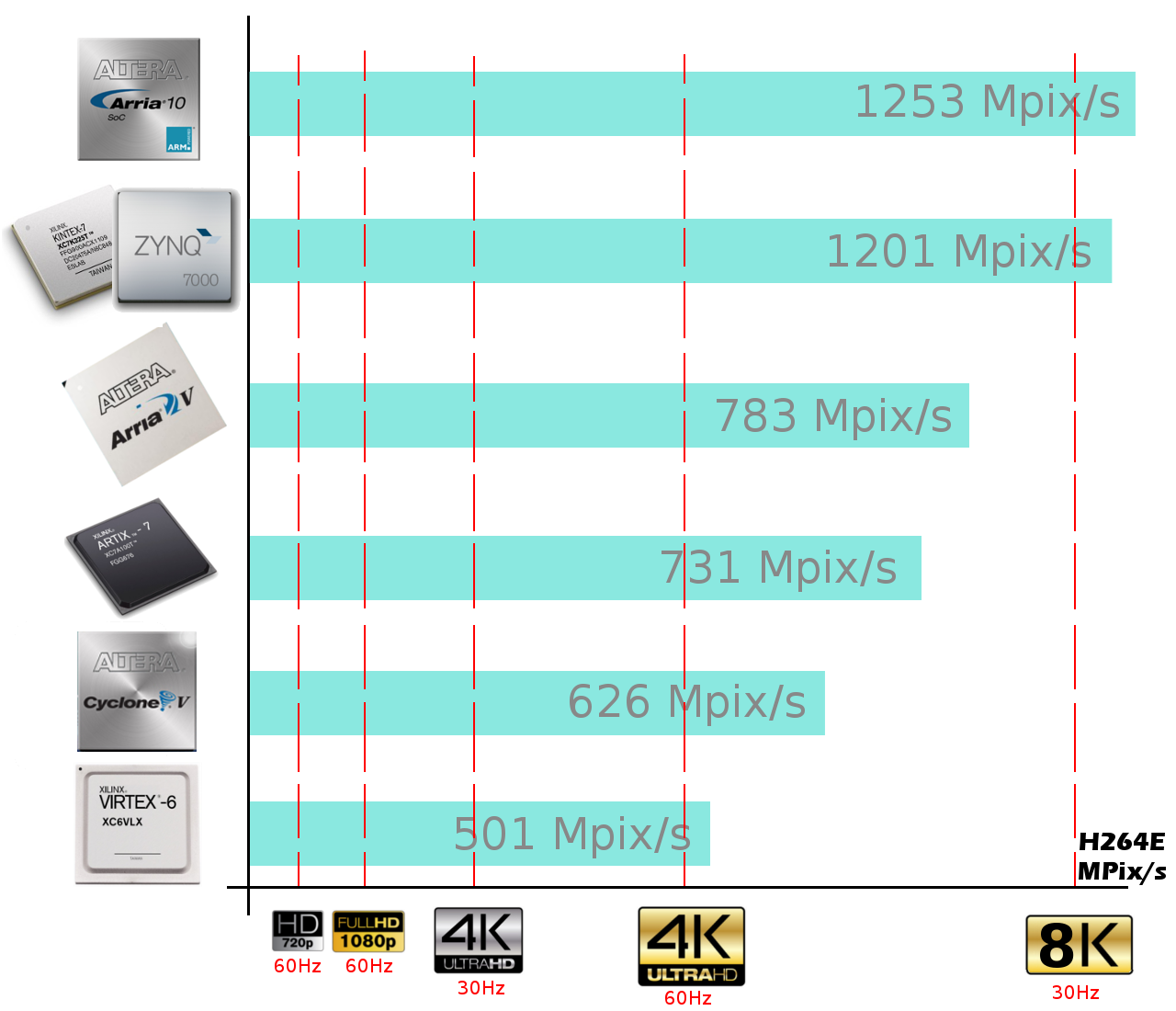

Welcome to our H.264 Encoder, a state-of-the-art solution for high-performance video compression. Designed to deliver the industry's highest pixel throughput, it's the only H.264 encoder that allows UltraHD 4K 60 on low-range FPGAs and 8K 30 on mid-range Arria 10 and Zynq FPGAs.

Choose Your Perfect Fit

We offer two encoder variants to meet your specific needs:

- H264E-I: A compact H.264 encoder that's perfect if you're looking for a smaller IP core with less compression. The standout feature of this variant is that it doesn't require external memory.

- H264E-P: If better compression is your goal, our H264E-P is a larger IP core that offers significantly superior compression.

Both variants are designed to deliver a processing speed of more than 5.2 pixels encoded per cycle, offering you high efficiency and throughput.

Features

Key Features:

-

Ultra-high-speed performance: Boasting the industry's highest constant throughput of 5.2 pixels encoded per clock cycle (0.19 clk/pix), our H.264 Encoder offers unparalleled speed.

-

Superior video quality: The encoder adheres to the ITU.T Rec. H.264 | ISO/IEC 14496-10 AVC video compression standard, ensuring top-tier video quality.

-

Versatile resolution support: Our H.264 Encoder has the capacity to support unlimited resolutions, from QVGA to 8K and beyond, using the same IP core.

-

Single Engine Design: With a single engine, our encoder results in the lowest possible latency, outperforming multi-engine alternatives.

-

Full Color Fidelity: Our encoder preserves full color fidelity with color subsampling 4:4:4 (also allowing for 4:2:2 and 4:2:0 inputs), ensuring vibrant and true-to-life colors.

Performance & Compatibility:

-

Impressive Frame Rates: The encoder can achieve 8K 30 fps on mid-range Intel Arria 10 and Xilinx Zynq FPGAs and UltraHD 4K 60 fps on low-end Artix-7 and Cyclone V FPGAs.

-

Efficient Parallel Encoding: The encoder is designed to handle up to 32 inputs encoded in parallel with a single instance, increasing efficiency and throughput.

-

Future-ready: With the option to encode beyond the maximum level (currently 6.2), our encoder is prepared to handle future H.264 specification revisions.

-

H.264 Profiles: High 4:4:4 Predictive Profile (H264E-P) and CAVLC 4:4:4 Intra Profile (H264E-I and H264E-P).

Flexibility & Control:

-

Real-time Control: The encoder features a real-time configurable VBR/CBR mode that automatically controls all H.264 parameters, providing users with greater control over video quality and file size.

-

Variable Frame Options: Our encoder supports a selectable number of predicted frames (P) per keyframe (I) and a selectable number of slices per frame, allowing for greater customization based on your needs.

-

Industry Standard Interfaces: We utilize AXI-Lite slave for configuration/status and AXI3/4 master for pixel-input/encoded-output, with optional AXI4-Stream Pixel-Input and Encoded-Output interfaces for greater compatibility and ease of use.

Additional Features:

-

Motion Estimation Support: Our H264E-P variant offers wide motion estimation support, providing better compression and video quality.

-

Latency Optimization: Our encoder boasts very low latency, taking only 16 lines' time from the first pixel input.

-

Convenient Output: The encoder outputs in Byte stream format (raw .264) for easier encapsulation and has options for full or pseudo-reconstructed decoded video outputs (H264E-P and H264E-I, respectively).

-

Hardware Efficiency: The encoder features embedded DMA engines in AXI3/4 interfaces for direct connection to a memory controller, and offers an optimized pixel input mode to boost shared memory efficiency.

You may also be interested in VISENGI's H.264 Decoder IP Core...

Interfaces

The data interfaces in the H.264 Encoder IP Core (H264E) use the AXI industry standard. The Master I/O data interfaces use an AXI3 bus, forward compatible with AXI4 interconnects.

The input/output interfaces of the H264E IP core are the following:

-

Configuration Interface: AXI-Lite slave with a 32 bits data interface to control all the necessary parameters of encoding.

-

Data I/O Interface: AXI3/4 Master interface with a data width of 128 bits for reading input pixels and writing H.264 encoded files from/to memory. Optional AXI4-Stream pixel input interface and AXI4-Stream coded video output.

-

H264E-P Reference I/O Interface: (H264E-P only) AXI3/4 Master interface with a data width of 128 bits, for reading/writing reference frames.

-

Motion Estimation Interface (only for H264E-P WME): Optional AXI3/4 Master read-only interface with a data width of 256 bits, used for reading reference frames from memory exclusively for motion estimation.

-

Interrupt output: Rising-edge interrupt to signal ends of frame and/or partial frame.

Interactive Evaluation Demo Video

Smallest FPGAs running H264E-P at common video modes

VISENGI's H264E-I and H264E-P's careful engineering not only encodes >5.2 pixels per clock cycle, it is also crafted to synthesize at higher clock frequencies than competitors' solutions. The result opens the world of 8K and Ultra HD 4K H264 encoding for FPGAs!

| Standard | Width x Height | Min. Pixel Throughput | Min. H264E Frequency | Smallest FPGA for H264E freq |

| HD 720p30 | 1280 x 720 | 28 Mpix/s | 6 MHz | Spartan-6 |

| HD 720p60 | 1280 x 720 | 56 Mpix/s | 12 MHz | Spartan-6 |

| FullHD 1080p30 | 1920 x 1080 | 63 Mpix/s | 13 MHz | Spartan-6 |

| FullHD 1080p60 | 1920 x 1080 | 125 Mpix/s | 25 MHz | Spartan-6 |

| UltraHD 4K 30 | 3840 x 2160 | 249 Mpix/s | 48 MHz | Spartan-6 |

| UltraHD 4K 60 | 3840 x 2160 | 498 Mpix/s | 96 MHz | Artix-7 / Cyclone V |

| 8K 30 | 7680 x 4320 | 996 Mpix/s | 192 MHz | Zynq / Arria 10 |

The actual input resolution is user-configurable and not limited to the ones listed above.

Resource Usage

In the next table you can find the synthesis results several FPGA vendors and families in which the core may be fitted. Please note that, since our designs are vendor and device independent, if your exact FPGA can not be found but it has enough resources compared to another FPGA, then it will doubtlessly also fit. In any case, if you would like to know the precise and up to date synthesis results for your specific FPGA or for ASIC targets, please contact us with your specific target.

| Vendor | Family | Spd | FF | LUT ALM | DSP | BRAM | Freq. | Throughput | Max.Res. |

|---|---|---|---|---|---|---|---|---|---|

| Vendor | Family | Spd | FF | LUT ALM | DSP | BRAM | Freq. | Throughput | Max.Res. |

| Xilinx | Virtex-6 | -1 | 44K | 54K | 32 | 122 | 96 MHz | 501 Mpix/s | 4K60 |

| Xilinx | Zynq 7030 | -1 | 44K | 54K | 32 | 122 | 166 MHz | 867 Mpix/s | 8K25 |

| Xilinx | Zynq 7030 | -2 | 44K | 54K | 32 | 122 | 200 MHz | 1044 Mpix/s | 8K30 |

| Xilinx | Zynq 7030 | -3 | 44K | 54K | 32 | 122 | 230 MHz | 1201 Mpix/s | 8K35 |

| Xilinx | Artix-7 | -1 | 44K | 54K | 32 | 122 | 100 MHz | 522 Mpix/s | 4K60 |

| Xilinx | Artix-7 | -2 | 44K | 54K | 32 | 122 | 124 MHz | 647 Mpix/s | 4K75 |

| Xilinx | Artix-7 | -3 | 44K | 54K | 32 | 122 | 140 MHz | 731 Mpix/s | 4K85 |

| Xilinx | Kintex-7 | -1 | 44K | 54K | 32 | 122 | 166 MHz | 867 Mpix/s | 8K25 |

| Xilinx | Kintex-7 | -2 | 44K | 54K | 32 | 122 | 200 MHz | 1044 Mpix/s | 8K30 |

| Xilinx | Kintex-7 | -3 | 44K | 54K | 32 | 122 | 230 MHz | 1201 Mpix/s | 8K35 |

| Xilinx | Spartan-6 | -2 | 44K | 66K | 32 | 139 | 52 MHz | 271 Mpix/s | 4K30 |

| Xilinx | Spartan-6 | -3 | 44K | 66K | 32 | 139 | 61 MHz | 318 Mpix/s | 4K35 |

| Intel | Cyclone III | C7 | 44K | 70K | 64 | 1.8 Mbit | 0 MHz | 0 Mpix/s | |

| Intel | Cyclone IV | C7 | 44K | 70K | 64 | 1.8 Mbit | 0 MHz | 0 Mpix/s | |

| Intel | Cyclone V | C6 | 44K | 35K | 32 | 1.8 Mbit | 120 MHz | 626 Mpix/s | 4K75 |

| Intel | Cyclone V | C7 | 44K | 35K | 32 | 1.8 Mbit | 100 MHz | 522 Mpix/s | 4K60 |

| Intel | Cyclone V | C8 | 44K | 35K | 32 | 1.8 Mbit | 85 MHz | 444 Mpix/s | 4K50 |

| Intel | Arria V | I3 | 44K | 35K | 32 | 1.8 Mbit | 150 MHz | 783 Mpix/s | 4K90 |

| Intel | Arria V | C5 | 44K | 35K | 32 | 1.8 Mbit | 128 MHz | 668 Mpix/s | 4K80 |

| Intel | Arria 10 | I2 | 44K | 35K | 32 | 1.8 Mbit | 210 MHz | 1097 Mpix/s | 8K30 |

| Intel | Arria 10 | I1 | 44K | 35K | 32 | 1.8 Mbit | 240 MHz | 1253 Mpix/s | 8K35 |

| Intel | Stratix IV | C2 | 44K | 50K | 64 | 1.8 Mbit | 148 MHz | 773 Mpix/s | 4K90 |

| Intel | Stratix V | C1 | 44K | 35K | 32 | 1.8 Mbit | 186 MHz | 971 Mpix/s | 8K25 |

Practical and methodology notes:

-

Standalone H264E-I IP core with AXI3 interfaces, 4K support, and max. compression. Smaller configurations available (less compression).

-

Results were obtained using the freely available versions of Xilinx Vivado and Intel Quartus environments.

-

Resource usage is subject to small changes due to further developments in quality/compression ratio.

Support

- Technical support via email

- IP Core Datasheet

- Xilinx Vivado drag'n'drop instance

- Intel Quartus drag'n'drop instance

- Linux driver source code for embedded setups

- Example SW source code control application

For any further information on this core or if you would like to receive a price quotation, please use the Contact form or the Quote Request button.

Download Product Brief

Download Product Brief