Features

This IP core has been developed to be a complete standards compliant JPEG / MJPEG Hardware Compressor / Encoder. Its main features are:

- Baseline DCT compression according to JPEG ITU-T T.81 | ISO/IEC 10918-1 standard.

- JFIF 1.02 standard file header.

- Drag'n'drop IP block for Xilinx Vivado Block Design and Altera Quartus Qsys.

- Constant throughput: 16 compressed pixels every 3 clock cycles: 5.3 pixels/cycle color and 8 pixels/cycle grayscale

- Industry standard interfaces: AXI-Lite slave for configuration/status and AXI3/4 master for pixel-input/encoded-output.

- Embedded DMA engines in AXI3/4 interfaces for direct connection to a memory controller. Support for high latency memories.

- Optional AXI4-Stream Pixel-Input and Encoded-Output interfaces.

- Optional optimized pixel input mode to boost shared memory efficiency.

- Optional SW control of the IP core configuration registers (sample source code provided)

- On-the-fly selectable quality level/compression ratio from 1 to 100 before every compression.

- Selectable JPG chroma subsampling (4:4:4, 4:2:2, 4:2:0), independent of input subsampling.

- Unlimited image resolution (up to 64K x 64K as per JPEG spec.).

- Support for RGB and YCbCr input pixels' color space

- Optional SW modules: Comment insertion support, Motion JPEG .avi format support.

- Unlimited Restart markers support.

- ASIC: On ASIC TSMC 0.13G process technology over 166 Mpix/s (>250 MHz)

If you are looking for HDR (up to 36bpp) you may be interested in VISENGI's JPEG Extended Encoder IP Core...

You may also be interested in VISENGI's M/JPEG Decoder IP Core...

Throughput

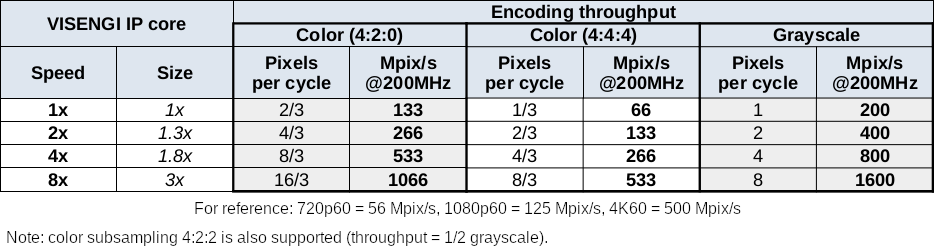

This IP core is available in 4 different speeds: 1x, 2x, 4x, and 8x. Each with a different relative size and licensing. The pixel throughputs are:

Above pixel throughputs (i.e. IP core frequency 200 MHz) are achieved on most of the latest mid-range FPGAs.

Grayscale pixels may be from 8 bits to up to 12 bits. Whereas color pixels may range from 24 to up to 36 bits per pixel. The speeds above remain constant in all cases.

Interfaces

The data interfaces in the JPEG Encoder IP Core (JPEGE) use the AXI industry standard. The Master I/O data interfaces use an AXI3 bus, forward compatible with AXI4 interconnects.

The input/output interfaces of the JPEGE IP core are the following:

-

Configuration Interface: AXI-Lite slave with a 32 bits interface to control all the necessary parameters of encoding.

-

Data I/O Interface: AXI3/4 Master interface for reading input pixels and writing .JPG files from/to memory. Optional AXI4-Stream pixel input interface and AXI4-Stream .JPG file output.

-

Interrupt output: A rising-edge interrupt is available, signaling when an image has been processed.

Quality Levels

In order to let you assess the properties of the on-the-fly selectable quality setting, please use the slider below the image (requires a fast connection) in order to see the final compressed image (real output from the JPEG encoder core at chroma subsampling 4:4:4 (best quality)) and compression ratio.

Quality Level(1-100):

PSNR: dB

File Size: bytes

Compression Ratio: : 1

Support

Included with the core is:

- Technical support via email

- IP Core Datasheet

- Xilinx Vivado drag'n'drop instance

- Altera Qsys drag'n'drop instance

- Linux driver for embedded setups

- Example SW control application

For any further information on this core or if you would like to receive a price quotation, please use the Contact form or the Quote Request button.